面向空间应用的AES加密算法如何在FPGA上的实现

随着国际空间任务的交叉合作以及互联网在空间任务中的应用,空间数据安全性受到威胁,空间数据文件加密日益受到设计人员的重视。国际空间数据系统咨询委员会已于2004年推荐AES加密算法作为空间数据系统的加密标准。那么我们今天就给大家讲讲面向空间应用的AES加密算法是如何在FPGA上的实现的。

一、AES加密算法及优化实现

1、AES加密算法

AES是一种可变密钥长度的迭代分组加密算法,明文被分成以128bit为一块进行加密,密钥长度可分别为128bit、192bit、256bit。

AES加密算法包括密钥扩展过程和加密过程。

加密过程又包括一个作为初始轮的初始密钥加法(AddRoundKey),接着进行若干次轮变换(Round),最后再使用一个轮变换(FinalRound),如下图所示。

明文可以表示为4*4B的状态矩阵,加密的每一轮是对状态矩阵进行操作,得到中间结果状态矩阵。初始变换指的是状态矩阵中每一列与初始密钥进行加运算。轮变换的每一轮包括字节替换(SubBytes)、行移位(Shiftrows)、列混合(Mixcolumns)、轮密钥加(AddRoundKey)。最后一轮变换不包括列混合(Mixcolumns)。经过最后一轮变换,中间状态矩阵将输出4*4B的密文。

密钥扩展是对给定初始密钥进行运算,得到每个轮变换的轮密钥。主要包括三步:字替换(Subword)、周期置换(Rotword)、圈常数字序列加运算。AES-128与AES-192密钥扩展的每一轮都包括三个步骤,对于AES-256,并不是每一轮都包括三个步骤,当密钥替换循环次数小于Nb*(Nr+1)(Nb数据块长度、Nr圈数),同时循环次数对Nk(密钥长度)取模的结果为4时,只进行字替换(Subword)。

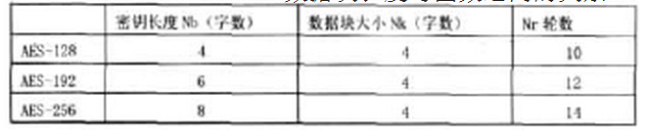

下表给出了三种AES加密的明文块长度,密钥长度,加密轮变换次数之间的关系。

2、AES加密算法优化实现

(1)字节替换(SubBytes)

SubBytes主要通过两步来完成,一步是在GF(28)中取乘法逆,另外一步是通过特别定义的GF(2)上的仿射作用。为了避免复杂的乘法运算,在FPGA上具体实现时,构造了16*16B的置换表,通过查表完成了字节替换,节省了运算时间。

(2)行移变换(shiftrows)

ShiftRows与列混合运算相互影响,在多轮变换后,使密码信息达到充分的混乱。行变换是在状态的每个行间进行的,是状态中的行按不同的偏移量进行循环左移运算。通过对每个字节的行移位实现该变换。

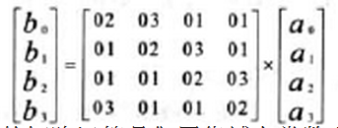

(3)列混合(MixColumns)

假设列混合运算输入为a,输出为b,加密的列混合运算可做如下表示:

式中所示的矩阵运算是伽罗华域上常数乘法运算。伽罗华域上乘以任何常数的乘法都可以通过反复的乘以02和异或运算来实现。将GF(28)域中的每一个元素与02的乘积存储在一张16*16B查找表中,通过异或运算和查表即可实现列混合运算。

(4)密钥加法(AddRoundKey)

AddRoundKey是将轮密钥中的各个字节与状态中的各个字节进行逐位异或运算,实现密码和密钥的混合。轮密钥是由初始密钥通过密钥扩展得到的。

(5)密钥扩展(KeyExpansion)

初始密钥和扩展后的整个密钥表可以看作是一个字(word)序列。密钥扩展是针对字进行的,为此又引入了两个对字进行处理的函数:字替代(Subword)和字旋转(RotWord)。字旋转将字的4个字节循环右移一个单位。密钥扩展还包括引入轮常数Rcon。字替换和引入轮常数均可使用查表法完成。字旋转可以用简单的交换字的顺序实现。

在FPGA的实现过程中,若不进行上述诸如查表法的优化,将会造成资源占用过度,运行速率低下的情况。

二、面向空间应用的AES加密算法在FPGA上的实现与仿真

1、面向空间应用的AES加密算法在FPGA上的实现方案

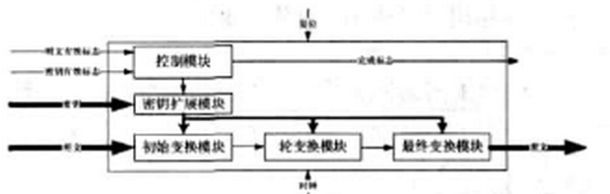

下图为面向空间应用的AES加密算法在FPGA上的实现框图,其中明文有效标志和密钥有效标志输入给控制模块,初始密钥送给密钥扩展模块,明文输入到初始变换模块。控制模块输出加密完成标志,最终变换模块输出密文。其中粗箭头为数据线,细箭头为控制线。为满足加密过程的时序要求,控制模块对输入的明文有效信号及密钥有效信号进行控制。密钥扩展模块在不同轮数下产生的扩展密钥分别送给初始变换模块,轮变换模块以及最终变换模块。初始变换模块对明文加了初始轮密钥;轮变换模块进行了四个变换步骤。最终变换模块与轮变换模块不同在于没有进行混合列操作。

2、仿真结果

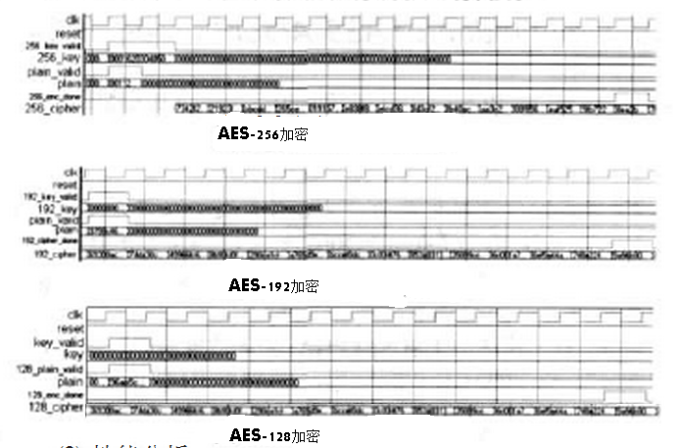

本设计采用VHDL语言,在Xilinx公司的一款FPGA上实现了AES加密算法。分别对AES-128、AES-192、AES-256加密算法实现进行仿真,在FPGA资源占用率、数据处理速率等方面进行了对比分析。

(1)仿真结果

下面几个图分别是AES-256、AES-192、AES-128的FPGA实现仿真结果,从图中可以看出AES-256可以在15个时钟周期内完成,AES-192可以在13个周期实现加密算法,AES-128可以在12个时钟周期内实现加密算法。

(2)性能分析

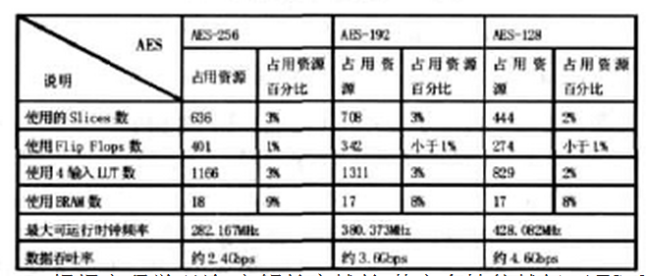

在Xilinx公司的一款X2V系列FPGA上所占用的资源情况对比如下表所示。

根据密码学理论,密钥长度越长,其安全性能越好。AES-256占用硬件资源较AES-128、AES-192多,但AES-256可以提供最好的安全性。

三种加密算法占用的资源数相当,数据吞吐率随着密钥长度加长而变小。

本文对AES加密算法进行了研究,提出了面向空间应用的AES加密算法的FPGA实现方案。通过仿真分析,表明利用FPGA进行AES进行数据文件加密具有占用硬件资源较少,数据吞吐率高,安全性好的特点,门数在10万左右的小型FPGA即可实现该加密算法。考虑到安全性,在实际应用中,AES-256加密算法是最适合的。

小知识之FPGA

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。